## ENGINEERING IN ADVANCED RESEARCH SCIENCE AND TECHNOLOGY

ISSN 2278-2566 Vol.02, Issue.03 May -2018 Pages: 174-179

# RELIABLE AND EFFICIENT POWER OPTIMIZED FFT PROCESSOR USING MODIFIED BOOTH ENCODING

## 1. SYED SHEHNAZ, 2. SUBHAKARA RAO B

1. M. tech, Dept. of ECE, Guntur Engineering College, Guntur, A.P. 2. Associate Professor, Dept. of ECE, Guntur Engineering College, Guntur, A.P.

**Abstract.** The primary objective of this project is to design a multi-way FFT reversal switch that has the probability of processing the paired data stream. Fast Fourier Transform (FFT) has become ubiquitous in many engineering applications. Nowadays, FFT is most widely used block in many communication and signal processing systems. This project presents a new FFT pipeline processor for the FFT calculation of two independent data streams. The FFT architecture of the multipath delay switch is used in the proposed architecture to process an N / 2 point decimation in FFT time and an N / 2 point decimation in frequency FFT operations of odd and even samples of two Data separately to reduce the area and high throughput. To achieve the best performance of the architecture using a modified cab algorithm to minimize area and time parameters.

**Keywords:** Fast Fourier transform (FFT), folding, parallel processing, pipelining, radix, real signals, register minimization, reordering circuit, Radix-8 modified booth encoding.

#### 1 Introduction:

The Fast Fourier Transform (FFT) is one of the prominent algorithms in the digital signal processing domain. It is used to compute the discrete Fourier transform (DFT) efficiently. In order to meet the high and real-time demands of modern applications, hardware designers have always tried to implement efficient architectures for FFT calculation. In this context, pipelined hardware architectures are used to simplify the FFT operations. Transmitter operations perform FFT operations. operations perform receiver operations. For the operating speed on the transmitter side to implement this new architecture to process both DIT and DIF simultaneously. A real-time pipeline FFT processor operates as a function of the single path delay feedback [1], a hardware-oriented rdix-22 algorithm is derived by integrating a twiddle factor decomposition technique into the division and conquest. The multi-mode multipath delay feedback architecture based on dynamic voltage The scaling program (DVFS) [2] uses to process the FFT processor for OFDM MIMO applications. To achieve the high throughput of the multi-mode FFT processor with flexible-variable delay (FRCMDF) feedback structure (FRCMDF) [3] for WLAN, WPAN, WMAN applications. [2] - [4] The architectures of the FFT processor do not have specific bit reversal circuits. The four independent data streams work independently using the MDC technique, but the outputs have not come parallel. [6] in these decimated dual channel delay transfer data switch units and integrated bit sequence converter, returns the various radixes to process the

pipeline FFT operations. [7] In this paper folding technique and register minimization techniques are used elaborate the pipelined parallel FFT operations. For different radixes, the series of data bit reversal circuits have been discussed in [8]. In this [9], the MDC and MDF methods with the organisation of the memory bank of the parallel circuit with reversed bits used. [10] Advanced architectures are used in this reorganisation The

circuit is applicable for a specific order. [11] Here SDC-SDF architectures combined to obtain only serial data transmission.

Idea of the working methodology:

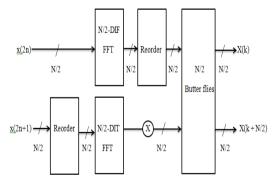

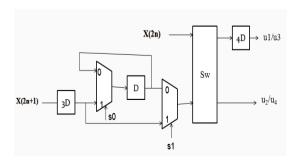

Fig. 1idea of the working methodology

The reorganisation blocks of FIG. 1 shows the odd samples N / 2 (x (2n + 1)) are rearranged before FIT DIT operation N / 2 point, and the even samples N

/ 2 (x (2)) are rearranged after the DIF N / 2 points FFT operation. In order to calculate the N-point DIT FFT from the outputs of two N / 2-point FFT, an additional step of the butterfly operations are performed on the results of the two FFTs. Thus, the outputs generated by an additional butterfly stage are in the natural order.

TABLE I

DATA FLOW THROUGH DIFFERENT LEVELS

| Level |         | TI      | ME —    |         |         |         |         |

|-------|---------|---------|---------|---------|---------|---------|---------|

| L1    | E1(1,1) | 01(1,1) | E1(1,2) | 01(2,1) |         |         |         |

| L2    |         | E1(2,1) | E2(2,1) | E1(2,2) | E2(2,2) |         |         |

| L3    |         |         | E1(3,1) | O1(3,1) | E1(3,1) | O1(3,2) |         |

| M1    |         | E2(1,1) | O2(1,1) | E2(1,2) | O2(1,2) |         |         |

| M2    |         |         | 01(2,1) | 02(2,1) | 01(2,2) | 02(2,2) |         |

| M3    |         |         |         | E2(3,1) | 02(3,1) | E2(3,2) | O2(3,2) |

Table 1 shows the L1, L2, L3, M1, M2, M3 here LI, M1 are two N / 2 bits of separation of the odd rearranged bits and equal data and L2 and M2 are butterfly operations performed and L3 and M3 is the last steps of the butterfly operation to rearrange the even bits to obtain outputs from normal order.

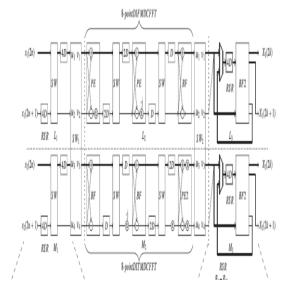

Fig2:16point radix-2 FFT architecture

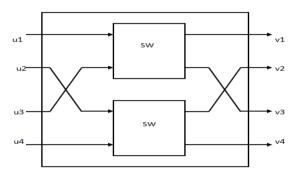

The FFT architecture in the figure above is divided into six levels (L1, L2, L3, M1, M2 and M3). The registers RSR in the levels L1 and M1 reorder the odd input data and the registers RSR in the levels L3 and M3 reorder the partially processed uniform data. FIFT DIF and DIT eight-point operations are performed in L2 and M2, respectively. Data from L1 and M1 can be transmitted to L2 and M2, respectively, or vice versa using SW1. Similarly, data from L2 and M2 can be transmitted to L3 and M3, respectively, or vice versa using SW2. SW1 and SW2 have two switches (SW) for exchanging the data path and propagating the data at different levels. During the normal mode, the switches (SW1 or SW2) pass the data to u1, u2, u3 and u4 to v1, v2, v3 and v4, respectively. However, during the swap mode, the switches (SW1 or SW2) pass the data to u1, u2, u3 and u4 to v3, v4, v1 and v2, respectively. SW1 is in swap mode during the first N / 2 clock cycles and is in normal mode during N / 2 + 1 to N. On the other hand, SW2 is in normal mode during the first clock cycles N / 2 and It is in swap mode during N / 2 + 1 to N. Thus, SW1 and SW2 are in different mode at all times and change mode for all N / 2 clock cycles. There is a data transition between L y and L y + 1 or My and My + 1 (where y may be 1 or 2), the switches (SW1 or SW2) are in normal mode, and if there is Transition Between L v and My + 1 or My and Ly + 1, then the switches (SW1) or SW2) are in swap mode. Like other control signals in the design, the control signals at switches SW1 and SW2 are externally supplied and these switch control signals exchange at each N / 2 clock cvcle.

Fig3: Internal structure of SW1 and SW2

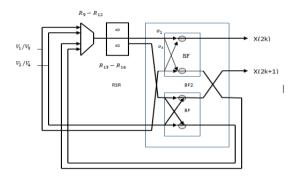

Fig4:Detailed structure of L3 and M3

Fig4: Structure of RSR in delay commutator unit in L1 and M1

The proposed architecture is inspired by the architecture in [7] where the N / 2 data planning records before the first butterfly unit are used to separate the odd samples from the even samples and delay them to generate x (n) and x (N + N / 2) in parallel. In the proposed architecture, these data planning registers are reused to retrieve inverted strong samples. Similarly, N / 2 data planning registers are used before the last butterfly unit to store partially processed even samples until odd samples arrive in [7] and here, these registers are reused to reverse Partially processed partial samples (DFT FFT outputs). In [8], circuits that use multiplexers and shift registers for bit inversion are proposed. If N is the equal power of r, then the number of registers required to invert the data N is  $(\sqrt{N} - 1)$  2. If N is the odd power of r then the number of registers required for Inverting the bit N is  $(\sqrt{r} N - 1) (\sqrt{N} / r - 1)$ , where r is the basis of the FFT algorithm. In the proposed architecture, these bit inversion circuits are incorporated into the data planning register to perform a dual role.

TABLE 2

Bit reversal operation in levels of L1 and M1

| Clk | X(2n) | X(2n+1) | Rı    | R2    | R3    | R4    | R٤   | R6   | R7   | R8   | μ3   | μ4    |

|-----|-------|---------|-------|-------|-------|-------|------|------|------|------|------|-------|

| 0   | X(0)  | X(1)    |       |       |       |       |      |      |      | -    |      |       |

| 1   | X(2)  | X(3)    | X(1)  | -     |       |       | X(0) |      |      | -    |      |       |

| 2   | X(4)  | X(5)    | X(3)  | X(1)  |       |       | X(2) | X(0) |      |      |      |       |

| 3   | X(6)  | X(7)    | X(5)  | X(3)  | X(1)  |       | X(4) | X(2) | X(0) | -    |      |       |

| 4   | X(8)  | X(9)    | X(7)  | X(5)  | X(3)  | X(1)  | X(6) | X(4) | X(2) | X(0) | X(0) | X(8)  |

| 5   | X(10) | X(11)   | X(9)  | X(7)  | X(5)  | X(3)  | X(1) | X(6) | X(4) | X(2) | X(2) | X(10) |

| 6   | X(12) | X(13)   | X(11) | X(9)  | X(7)  | X(5)  | X(5) | X(1) | X(6) | X(4) | X(4) | X(12) |

| 7   | X(14) | X(15)   | X(13) | X(11) | X(9)  | X(7)  | X(3) | X(5) | X(1) | X(6) | X(6) | X(14) |

| 8   | -     |         | X(15) | X(13) | X(11) | X(9)  | X(7) | X(3) | X(5) | X(1) | X(1) | X(9)  |

| 9   | -     |         | -     | X(15) | X(13) | X(11) |      | X(7) | X(3) | X(5) | X(5) | X(13) |

| 10  | -     |         |       |       | X(15) | X(13) |      |      | X(7) | X(3) | X(3) | X(11) |

| 11  | -     |         |       |       |       | X(15) |      |      |      | X(7) | X(7) | X(15) |

TABLE 3

Bit reversal operation in levels of L3 and M3

| Clk | V3   | V4   | R9   | R10  | R11  | R12  | R13  | R14  | R15  | R16  | 1    | 1     |

|-----|------|------|------|------|------|------|------|------|------|------|------|-------|

| 0   | X(0) | X(4) |      |      |      |      |      |      |      |      |      |       |

| 1   | X(1) | X(5) | X(0) |      |      |      | X(4) |      |      |      |      |       |

| 2   | X(2) | X(6) | X(1) | X(0) |      |      | X(5) | X(4) |      |      |      |       |

| 3   | X(3) | X(7) | X(2) | X(1) | X(0) |      | X(6) | X(5) | X(4) |      |      |       |

| 4   |      |      | X(3) | X(2) | X(2) | X(0) | X(7) | X(6) | X(5) | X(4) | X(0) | X(8)  |

| 5   |      |      |      | X(3) | X(3) | X(1) |      | X(7) | X(6) | X(5) | X(4) | X(12) |

| 6   |      |      |      |      | X(4) | X(2) |      |      | X(7) | X(6) | X(2) | X(10) |

| 7   |      |      |      |      | -    | X(3) |      |      |      | X(7) | X(6) | X(14) |

#### PROPOSED ARCHITECTURE

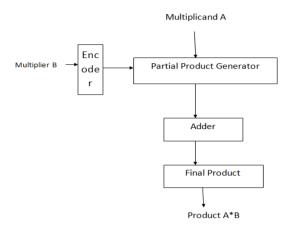

## RADIX-8 MODIFIED BOOTH ALGORITHM:

The Booth algorithm consists of repeatedly adding one of two predetermined values to a product P and Then performing an arithmetic shift to the right on P.

The multiplier architecture consists of two architectures, i.e., Modified Booth. By the study of different multiplier architectures, we find that Modified Booth increases the speed because it reduces the partial products by half. Also, the delay in the multiplier can be reduced by using Wallace tree. The energy consumption of the Wallace Tree Multiplier is also lower than the Booth and the array. The characteristics of the two multipliers can be combined to produce a high-speed and lowpower multiplier. The modified stand-alone multiplier consists of a modified recorder (MBR). MBR has two parts, i.e., Booth Encoder (BE) and Booth Selector (BS). The operation of BE is to decode the multiplier signal, and the output is used by BS to produce the partial product. Then, the partial products are added to the Wallace tree adders, similar to the carry-save-adder approach. The last transfer and sum output line are added by a carry look- ahead adder, the carry being stretched to the left bv positioning.

|               |                    | 0 |

|---------------|--------------------|---|

| Quartet value | Signed-digit value | _ |

| 0000          | 0                  | _ |

| 0001          | +1                 |   |

| 0010          | +1                 |   |

| 0011          | +2                 |   |

| 0100          | +2                 |   |

| 0101          | +3                 |   |

| 0110          | +3                 |   |

| 0111          | +4                 |   |

| 1000          | -4                 |   |

| 1001          | -3                 |   |

| 1010          | -3                 |   |

| 1011          | -2                 |   |

| 1100          | -2                 |   |

| 1101          | -1                 |   |

| 1110          | -1                 |   |

| 1111          | 0                  |   |

|               | •                  |   |

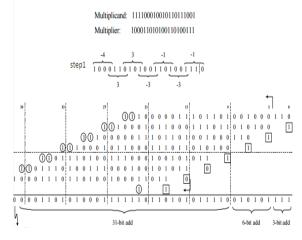

Here we have a multiplication multiplier, 3Y, which is not immediately available. To Generate it, we must run the previous addition operation: 2Y + Y = 3Y. But we are designing a multiplier for specific purposes and then the multiplier belongs to a set of previously known numbers stored in a memory

chip. We have tried to take advantage of this fact, to relieve the radix-8 bottleneck, that is, 3Y generation. In this way, we try to obtain a better overall multiplication time or at least comparable to the time, we can obtain using a radix-4 architecture (with the added benefit of using fewer transistors). To generate 3Y with 21-bit words you just have to add 2Y + Y, ie add the number with the same number moved to a left position.

A product formed by multiplying it with a multiplier digit when the multiplier has many digits. Partial products are calculated as intermediate steps in the calculation of larger products.

The partial product generator is designed to produce the product multiplying by multiplying A by 0, 1, -1, 2, -2, -3, -4, 3, 4. Multiply by zero implies that the product is "0". Multiply by" 1 "means that the product remains the same as the multiplier. Multiply by "-1" means that the product is the complementary form of the number of two. Multiplying with "-2" is to move left one as this rest as per table.

#### SIGN EXTENSION CORRECTOR:

The Sign Extension Corrector is designed to increase the Booth multiplier capacity by multiplying not only the unsigned number but also the signed number. The principle of the sign extension that converts the signed multiplier not signed as follows. When unsign is signalled s\_u = 0, it indicates the multiplication of the unsigned number and when s\_u = 1, it shows the multiplication of the signed number. When a bit signal is called unsigned bit (s\_u), it is indicated whether the multiplication operation is an unsigned number or number.

| Sign-unsign | Type of operation       |

|-------------|-------------------------|

| 0           | Unsigned multiplication |

| 1           | Signed multiplication   |

### Example:

|                      |       |             |              |              | 2,299,30 | )ps   |          |       |          |       |          |       |              |              |                                                  |                                                  |          |          |

|----------------------|-------|-------------|--------------|--------------|----------|-------|----------|-------|----------|-------|----------|-------|--------------|--------------|--------------------------------------------------|--------------------------------------------------|----------|----------|

| Name                 | Value |             | 2,299,200 ps | 2,299,250 ps | 2,299,30 | lps   | 2,299,39 | l ps  | 2,299,40 | lps   | 2,299,45 | )ps   | 2,299,500 ps | 2,299,550 ps | P,299,600 ps                                     | 2,299,650 ps                                     | 2,299,70 | Úps      |

| le sel               | 0     |             |              |              | -        |       | iii      |       | _        |       | _        |       |              |              | <del>                                     </del> | <del>                                     </del> | ۳        | ÷        |

| le dk                | 1     | Т           |              |              |          | П     |          |       |          |       |          | П     |              |              |                                                  |                                                  |          | ī        |

| T <sub>e</sub> rst   | 0     |             |              |              |          |       |          |       |          |       |          |       |              |              |                                                  |                                                  |          |          |

| <b>₩</b> co()50)     | 16    |             | 0            |              | 16       | 3     | 0        | 9     | 22       | -6    | 4        | 9     |              |              | 1                                                |                                                  | 15       | 3        |

| <b>₩</b> co1050      | 248   |             | 0            |              | 248      | 20    | T        | 4     | 250      | 1     | 240      | 6     |              |              | 1                                                |                                                  | 248      | 10       |

| <b>₩</b> 002[150]    | 0     |             | 0            |              | 0        | 1     |          |       | П        | 0     | 1        | 1     |              |              |                                                  |                                                  | 0        | 0        |

| <b>₩</b> 068[150]    | 0     |             | 0            |              | 1        | 1     |          | ī     | П        | 0     | T        | 0     |              |              |                                                  |                                                  | 0        | 0        |

| <b>₩</b> 004[350]    | 8     |             | 0            |              | ŝ        | +     |          | 5552  | 6        | 6553H | 15       | 65530 |              |              |                                                  |                                                  | 8        | 4        |

| <b>₩</b> 005[350]    | 248   |             | 0            |              | 248      | Ш     |          | 4     | 250      | 1     | 20       | 5     |              |              |                                                  |                                                  | 28       | N        |

| <b>▶</b> ∰ 06(150)   | 0     |             | 0            |              | I        | ī     |          | T     | T        | Ī     | ī        | T     |              |              |                                                  |                                                  | 0        | Œ        |

| <b>▶ 1 co</b> 7[150] | 0     |             | 0            |              | 1        | Ī     |          | Ī     | ī        | 1     | ī        | 1     |              |              | 1                                                |                                                  | 0        | 0        |

| op02(150)            | 16    |             | 0            |              | 16       |       |          | 9     | 2        | 6     | 4        | 9     |              |              |                                                  |                                                  | 15       | <u> </u> |

| <b>₩</b> 0,012,150]  | 0     |             | 0            |              | 1        | 1     |          | 0     | I        | 0     | 0        | 0     |              |              |                                                  |                                                  | 0        | 0        |

| ▶ # op22350]         | 8     |             | 0            |              | 8        | 4     | 0        | ×     | 6        | 254   | 15       | 250   |              |              | 1                                                |                                                  | 8        | 4        |

| ▶ # 0632[50]         | 0     |             | 0            |              | 1        | 1     | u        | 0     | T        | 0     | 1        | 0     |              |              | 1                                                |                                                  | 0        | 0        |

| <b>▶</b> ∰ 0942050]  | 65528 |             | 0            |              | 65528    | 65532 |          | 4     | 65530    | 1     | 5553     | 6     |              |              | 1                                                |                                                  | 65528    | 6.       |

| <b>▶</b> 🖁 0052050]  | 0     |             | 0            |              | 1        | 1     |          | 0     | I        | 1     | 1        | 1     |              |              | 1                                                |                                                  | 0        | 0        |

| <b>▶</b> 🖁 op62(150) | 65528 |             | 0            |              | 65528    | 6550  |          | 65284 | 65530    | 65282 | 65520    | 6526  |              |              | 1                                                |                                                  | 65528    | (6       |

| <b>▶</b> # cp72050]  | 0     |             | 0            |              | 1        | 1     |          | 0     | I        | 0     | I        | 0     |              |              |                                                  |                                                  | 0        | 0        |

| ▶ 🖁 swop0(15)        | 16    |             | 0            |              | 16       | 2     | 4        | 2     | 22       | 46    | 4        | 20    |              |              |                                                  |                                                  | 15       | 2        |

| <b>▶</b> # swop1[15: | Û     |             | 0            |              | 1        | 1     | •        | 0     |          | 0     | 0        | 0     |              |              |                                                  |                                                  | 0        | 0        |

| ► # swop2[15:1       | 16    |             | 0            |              | 16       | 3     | 4        | Ω     | 22       | 46    | 4        | 78    |              |              |                                                  |                                                  | 15       | 3        |

| ▶ 🖁 swop3(55         | 16    |             | 0            |              | 16       | 3     | 4        | Ω     | 22       | -16   | 4        | 78    |              |              |                                                  |                                                  | 15       | 3        |

| <b>▶ ₩</b> 5NOp4]15s |       |             | 0            |              | 1        | 1     |          | 0     | I        | 1     | 1        | 1     |              |              |                                                  |                                                  | 0        | (        |

| <u>. Hrsr</u>        | -     |             | Δ.           |              | Λ        | 1     | 4        | 1     |          | Α     | 1        | Α     |              |              |                                                  |                                                  | Δ        | V        |

|                      |       | X1: 2,299,3 | 00 m         |              |          |       |          |       |          |       |          |       |              |              |                                                  |                                                  |          |          |

|                      |       |             | ,*           |              |          |       |          |       |          |       |          |       |              |              |                                                  |                                                  |          |          |

#### **CONCLUSION:**

In this article, several FFT architectures are designed and simulated using VERILOG HDL. Power dissipation and fan-out conditions are calculated on different devices using the XILINX tool. The proposed processor simultaneously process two independent data streams and make it suitable for many real-time high-speed applications. The bit inversion circuit present in the previous drawings is eliminated by integrating two FFT processors, and the logs that are present in the architecture are reused for bit reversal. As a result, it avoids the need for additional registers to reduce inverted outputs. Additionally, the proposed architecture offers a higher throughput than previous architectures.

## REFERENCES:

- [1] N. Jiang and D. Harris, —Parallelized Radix-2 Scalable Montgomery Multiplier, submitted to IFIP Intl. Conf. on VLSI, 2007.

- [2] D. Kudeeth., —Implementation of low-power multipliers, Journal of low-power electronics, vol. 2, 5-11, 2006.

- [3] Y.N. Ching, —Low-power high-speed multipliers, IEEE Transactions on Computers, vol. 54, no. 3, pp. 355-361, 2005.

- [4] D. Harris, R. Krishnamurthy, M. Anders, S. Mathew, and S. Hsu, —An improved unified scalable radix-2 Montgomery multiplier, Proc. 17th IEEE Symp. Computer Arithmetic, pp. 172-178, 2005.

- [5] K. Kelley and D. Harris, —Parallelized very high radix scalable Montgomery multipliers, Proc. Asilomar Conf. Signals, Systems, and Computers, pp. 1196-1200, Nov. 2005.

- [6] J. Hensley, A. Lastra and M. Singh, —An area and energy efficient asynchronous booth multiplier for mobile devices, In Proc. Int. Conf. Computer Design (ICCD), 2004.

- [7] A. Efthymiou, W. Suntiamorntut, J. Garside, and L. Brackenbury. —An asynchronous, iterative implementation of the original Booth multiplication algorithm. In Proc. Int. Sympl, On

Advanced Research in Asynchronous Circuits and Systems, pages 207–215. IEEE Computer Society Press, Apr. 2004.

- [8] P. D. Chidgupkar and M. T. Karad, —The Implementation of Vedic Algorithms in Digital Signal Processing, Global J. of Engg. Edu, vol. 8, no.

- 2, pp. 153-158, 2004.

- [9] M. Sheplie, —High performance array multiplier, IEEE transactions on very large scale integration systems, vol. 12, no. 3, pp. 320-325, 2004.

- [10] Hsin Lei Lin, Robert C. Chang, Ming-Tsai, —Design of a Novel Radix-4 Booth Multiplier, IEEE Asia-Pacific Conference on Circuits and Systems, December 6-9, 2004.

- [11] A. S. Prabhu, and V. Elakya, —Design of Modified Low Power Booth Multiplier, IEEE Conference Publication, pp 1-6, 2012.